Introduction

다른 PC에서 아무런 문제없이 사용한 Vivado Project를 가져와서 Synthesis를 진행하였을 때 "Multiple block runs Failed"라는 message가 발생하는 경우가 있습니다. 이러한 문제가 발생하였을 때 원인과 해경방법에 대하여 알아보겠습니다.

Test를 위한 PC 사용환경은 다음과 같습니다.

- OS : Windows 10 pro ( version : 21H2 )

- Vivado version : 2022.1

Multiple block runs Failed

1.

Implementation까지 Error없이 진행했던 Vivado project를 다른 PC로 가져왔을 경우에, 사용 중인 IP에 대하여 "Regenerate Output Products"를 실행하면 Vivado 상단 오른 쪽에 "Multiple block runs Failed"라는 message가 발생하는 경우가 있습니다.

2.

이 경우, Vivado project가 있는 폴더의 "project_1.runs" 폴더를 삭제한 후에, 사용 중인 IP에 대한 "Regenerate Output Products"를 실행하여도 "Multiple block runs Failed"라는 message가 동일하게 발생합니다.

3.

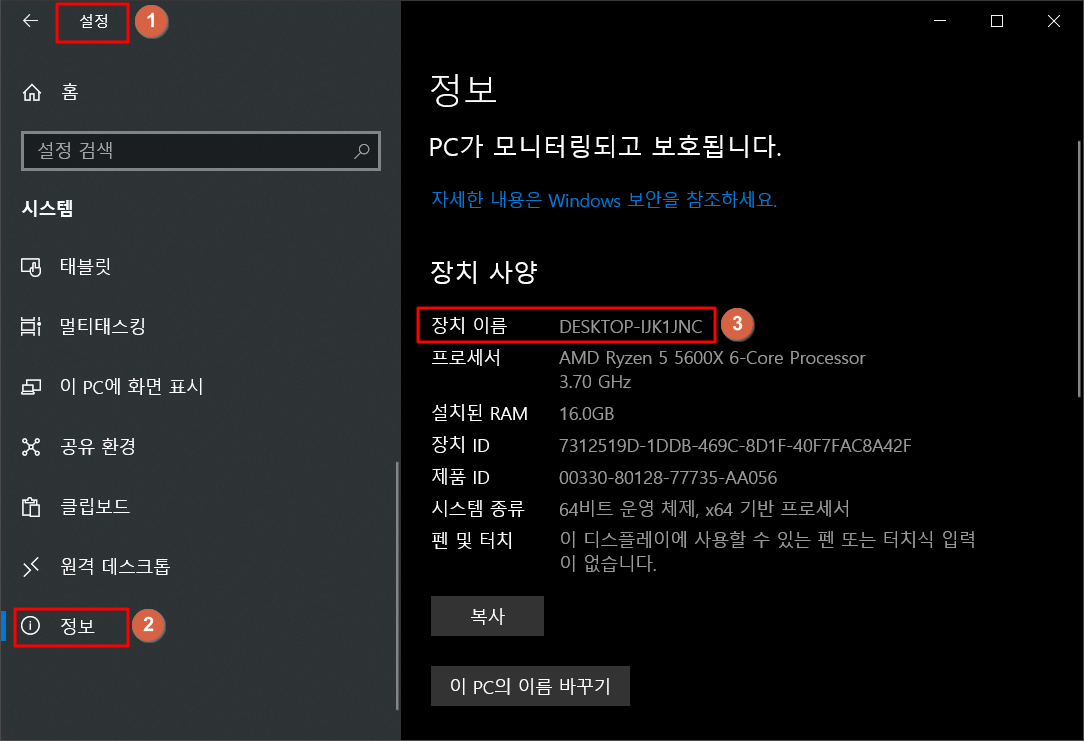

"Multiple block runs Failed"라는 message가 발생하는 이유는 컴퓨터의 장치 이름이 영어가 아닌 한글인 경우에 발생합니다.

Windows 10 OS에서 설정의 정보란을 보면 아래의 그림과 같이 컴퓨터의 장치 이름을 확인할 수 있습니다.

4.

컴퓨터의 장치 이름을 변경할 경우는 아래와 같이 "이 PC의 이름 바꾸기" 버튼을 클릭하여 수정합니다.

5.

Vivado tool은 한글 OS에 대한 호환성 테스트를 하지 않습니다. 그러므로 컴퓨터의 로그인 ID도 영어가 아닌 한글을 사용하여야 합니다. 가장 좋은 방법은 영문 OS를 사용하는 것 입니다.

지금까지 "Multiple block runs Failed"라는 message가 발생했을 경우에 원인과 해결방법에 대하여 알아보았습니다.

여러분의 FPGA 설계에 조금이라도 도움이 되었으면 합니다.

오늘도 좋은 하루 되세요.

(공감, 구독, 댓글은 저에게 힘이 됩니다!)

Create Date: September 28, 2022

Posted By: Mouessee

Xilinx 본사는 한국 내에 Corporate and Sales Distributor로 MAKUS를 두고 있습니다.

Xilinx 국내 Corporate and Sales Distributor인 MAKUS는 XIlinx FPGA Device를 기술영업을 통해 판매하며 기술지원이 가능합니다.

MAKUS www.makus.co.kr

관련 BLOG

------------------------------

------------------------------

Power Guide for Xilinx FPGAs

Introduction Xilinx Device를 사용함에 있어 대부분의 경우, Target Device에 대한 Power 설계에 대한 고민을 많이 합니다. 여기서는 Power Guide for Xilinx FPGAs에 대한 2가지 방법을 설명하려고 합니다...

740280.tistory.com

GTH의 reference Input Clock과 Data line rate 계산 방법

GTH의 reference Input Clock과 Data line rate 계산 방법

Introduction GTH를 사용할 경우 Reference input clock frequency와 Data line rate이 필요합니다. 여기서는 Reference input clock frequency와 Data line rate 사이에 어떠한 계산식으로 값이 결정되는지 알..

740280.tistory.com

'Xilinx > Vivado' 카테고리의 다른 글

| How to save simulation "waveform" result in Vivado (0) | 2023.02.14 |

|---|---|

| How to get & set up Vivado License (0) | 2023.02.09 |

| Little / Big Endian과 MSB-First, LSB-First의 의미 (0) | 2022.09.08 |

| Warning message occurred when installing Vivado 2022.1 (0) | 2022.09.06 |

| How to monitor XADC with "JTAG to AXI Master" IP (0) | 2022.08.31 |