Introduction

Vivado Tool에서 Simulation을 하려면 Verilog 혹은 VHDL로 Testbench file이 필요합니다. 하지만 아주 간단한 simulation을 위하여 Testbench file이 없어도 Simulation이 가능합니다. 이를 위하여 Vivado Tool은 add_force, remove_forces 등의 Tcl command를 제공합니다.

여기서는 Testbench file 없이 add_force, remove_forces 등의 Tcl command를 이용하여 Vivado에서 Simulation을 하는 방법을 설명하겠습니다.

Test를 위한 PC 사용환경은 다음과 같습니다.

- OS : Windows 10 pro ( version : 21H2 )

- Vivado version : 2022.1

How to run a Simulation without Testbench file in Vivado

1.

Test 환경은 다음과 같습니다.

- OS : Windows 10 pro

- Vivado version : 2020.1.1

2.

사용된 source code는 다음과 같습니다. 간단한 2 input AND gate입니다.

아래 "test.v"를 클릭하면 위 source code를 Dwonloaad 받을 수 있습니다.

3.

위 "test.v"을 사용하여 Vivado Project를 만듭니다. 그리고 Testbench file 없이 아래와 같이 "Run Behavioral Simulation"을 클릭합니다.

4.

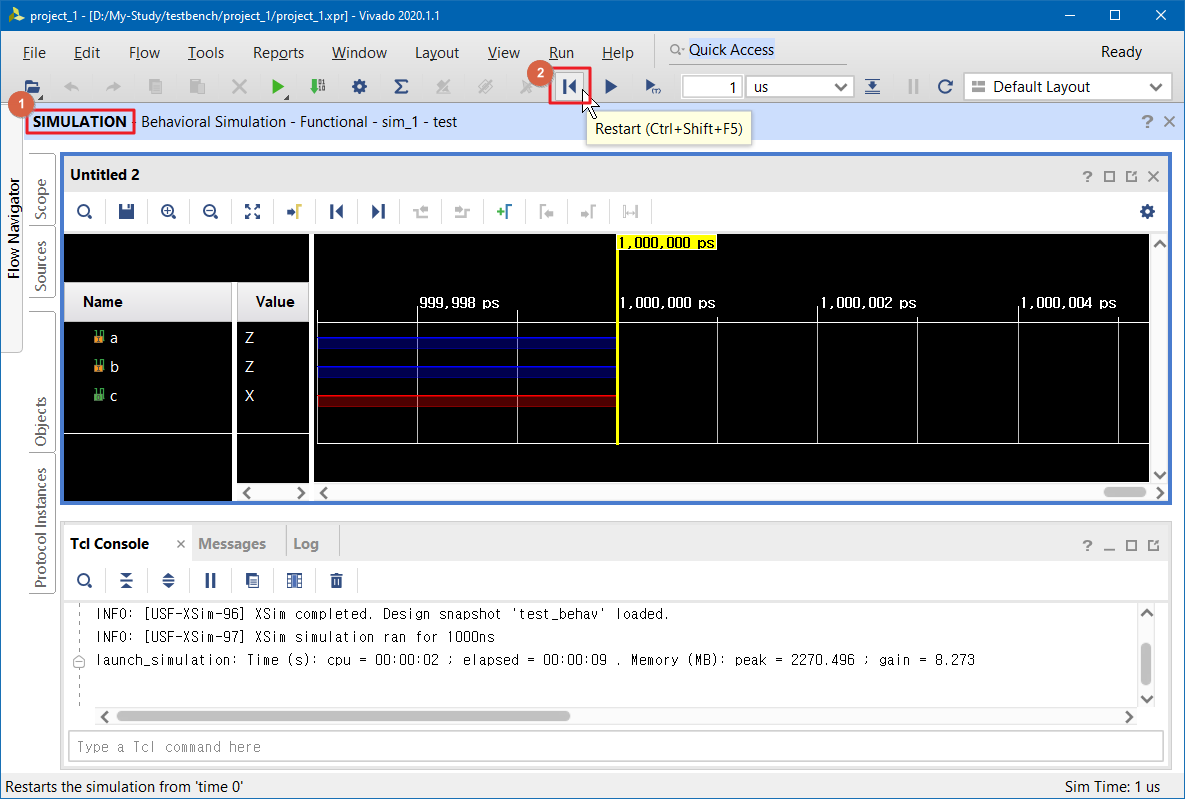

Vivado에서 SIMULATION 창이 띄워지면 "Restart" 아이콘을 클릭합니다.

5.

Tcl Console에 다음과 같이 2개의 "add_force" command를 기입합니다. 이후, Simaultion "Run" 아이콘을 클릭한 후, "Zoom Fit" 아이콘을 클릭합니다. Output c에 대한 출력 파형을 확인할 수 있습니다.

| add_force {/test/a} -radix bin {1 0ns} {0 200ns} {1 400ns} {0 600ns} {1 800ns} |

| test.v의 input a에 0ns에서 '1', 200ns에서 '0', 400ns에서 '1', 600ns에서 '0', 800ns에서 '1'이 되는 파형을 입력한다는 의미입니다. |

| add_force {/test/b} -radix bin {0 0ns} {1 300ns} {0 600ns} {1 900ns} |

| test.v의 input a에 0ns에서 '0', 300ns에서 '1', 600ns에서 '0', 900ns에서 '1'이 되는 파형을 입력한다는 의미입니다. |

( 아래의 그림은 반복되는 animated GIF 입니다. )

6.

처음부터 다시 시작할 경우는 아래와 같이 "Restart" 아이콘을 클릭한 후, Tcl Console에 "remove_forces -all"을 기입합니다. 이후에 "add_force"를 이용한 command를 기입하여 simulation을 합니다.

7.

추가 Tip !

clock 파형을 입력할 경우는 다음과 같습니다.

| add_force {/test/clk} -radix bin {1 0ns} {0 5ns} -repeat_every 10ns -cancel_after 1000ns |

| High 5ns, Low 5ns의 10ns period를 가지는 clock 파형을 1000ns까지 입력하는 command 입니다. |

8.

아래는 위에서 사용한 Tcl command file입니다.

아래는 위에서 사용한 Vivado 2020.1.1 project file입니다.

9.

"add_force", "remove_forces"에 대하여 보다 자세한 내용은 아래의 링크 내용을 보세요.

지금까지 Testbench file 없이 add_force, remove_forces 등의 Tcl command를 이용하여 Vivado에서 Simulation을 하는 방법에 대하여 알아보았습니다.

여러분의 FPGA 설계에 조금이라도 도움이 되었으면 합니다.

오늘도 좋은 하루 되세요.

(공감, 구독, 댓글은 저에게 힘이 됩니다!)

Feb 21, 2023

Posted By: Mouessee

Xilinx 본사는 한국 내에 Corporate and Sales Distributor로 MAKUS를 두고 있습니다.

Xilinx 국내 Corporate and Sales Distributor인 MAKUS는 XIlinx FPGA Device를 기술영업을 통해 판매하며 기술지원이 가능합니다.

MAKUS www.makus.co.kr

관련 BLOG

------------------------------

------------------------------

'Xilinx > Vivado' 카테고리의 다른 글

| CIPS IP must be included in every Versal ACAP design (0) | 2023.06.09 |

|---|---|

| How to use HDL Parameters for Interface Inference in a RTL Module (0) | 2023.02.21 |

| How to save simulation "waveform" result in Vivado (0) | 2023.02.14 |

| How to get & set up Vivado License (0) | 2023.02.09 |

| Multiple block runs Failed (0) | 2022.09.29 |