Introduction

디스플레이포트(DisplayPort)는 VESA(Video Electronics Standards Association)에 의해 제정된 디지털 디스플레이 인터페이스 표준으로 비디오 소스를 컴퓨터 모니터와 같은 디스플레이 장치에 전송하는 용도로 사용됩니다.

DisplayPort Connect는 총 20개의 Pins으로 구성되어 있습니다. 그중 중요한 pin이 data pin과 clock pin입니다. clock 1-pair, data 3-pair로 구성됩니다. (일반적으로 data 1-pair를 1 lane이라고 합니다.)

그리고 DisplayPort는 version에 따라 1 lane의 전송 속도가 다릅니다. 그러므로 어떤 version의 DisplayPort를 개발하느냐에 따라 사용하려는 Xilinx Device의 Gigabit Transceiver의 1 lane의 최대 전송 속도를 검토하여야 합니다. ( Xilinx Device는 device family, speed garde, device package에 따라 Gigabit Transceiver의 1 lane의 최대 전송 속도에 차이가 있습니다.)

Table of Contents

01 : DisplayPort version 별로 1 lane의 data rate에 대한 Spec.

02 : Xilinx DisplayPort Subsystem IP

03 : Xilinx Device Family 별 DC and AC Switching Characteristics

04 : 128B/132B

05 : Reference

DisplayPort version 별로 1 lane의 data rate에 대한 Spec.

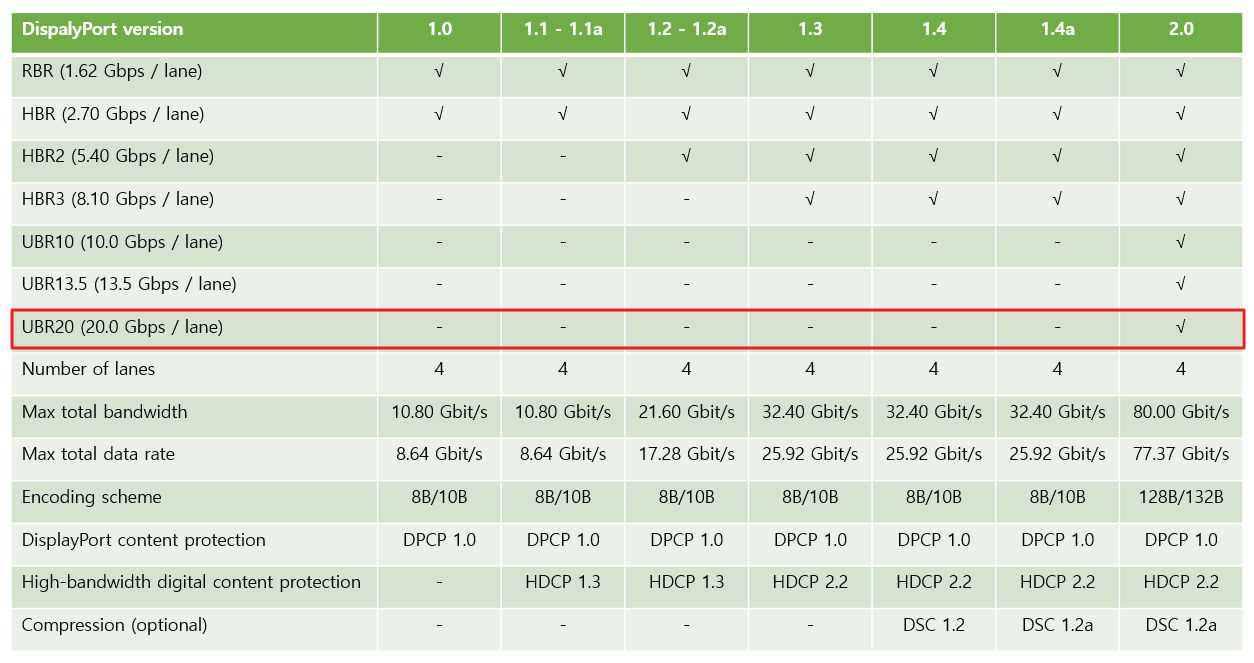

아래의 표를 보면 DisplayPort version별로 1 lane의 data rate에 대한 spec을 확인할 수 있습니다.

VESA DisplayPort standard 2.0의 경우 최대 20.0 Gbps / lane임을 알 수 있습니다.

아래 링크의 사이트에서 보다 자세한 내용을 확인할 수 있습니다.

(Web-site) WIKIPEDIA - DisplayPort

DisplayPort - Wikipedia

From Wikipedia, the free encyclopedia Jump to navigation Jump to search Digital display interface DisplayPort Type Digital audio/video connectorProduction historyDesigner VESADesigned May 2006Manufacturer VariousProduced 2008–presentSuperseded DVI, VGA,

en.wikipedia.org

Xilinx DisplayPort Subsystem IP

Xilinx는 DisplayPort에 대하여 DisplayPort Subsystem이라는 이름으로 IP를 제공하고 있습니다.

아쉽게도 유료입니다. 가격 문의는 Xilinx 국내(Korea) 대리점인 MAKUS로 문의가 가능합니다.

Xilinx DisplayPort Subsystem / Part Number: EF-DI-DISPLAYPORT-SITE

DisplayPort Subsystem

The Xilinx DisplayPort® Subsystem interconnect protocol is for transmission and reception of serial-digital video at two standard rates of 1.6Gbps and 2.7Gbps for consumer and professional displays.

www.xilinx.com

1.

VESA DisplayPort standard 1.2a을 위하여 아래 2개의 Xilinx 문서를 참고하면 됩니다.

(PDF) PG233 June 3, 2020 - DisplayPort RX Subsystem v2.1

(PDF) PG199 June 17, 2019 - DisplayPort TX Subsystem v2.1

2.

VESA DisplayPort standard 1.4 (Supports eDP v1.4b)을 위하여 아래 2개의 Xilinx 문서를 참고하면 됩니다.

(PDF) PG300 (v2.1) August 31, 2020 - DisplayPort 1.4 RX Subsystem v2.1

(PDF) PG299 (v2.1) August 31, 2020 - DisplayPort 1.4 TX Subsystem v2.1

위 PG300, PG299 문서의 각 6~7페이지를 보면 Device Fmily, Speed Grade 별 Gigabit Transceiver의 1 lane의 최대 전송 속도에 대한 정보를 확인할 수 있습니다.

3.

VESA DisplayPort standard 2.0에 대하여 Xilinx DisplayPort Subsystem IP는 Not Support 입니다.

이 부분에 대하여 추후 Update 된 내용이 있다면 다시 설명하도록 하겠습니다.

Xilinx Device Family 별 DC and AC Switching Characteristics

Xilinx Device는 device family, speed garde, device package에 따라 Gigabit Transceiver의 1 lane의 최대 전송 속도에 차이가 있습니다. 이에 대한 자세한 정보를 확인하려면 사용하려는 Device의 DC and AC Switching Characteristics 문서를 살펴보아야 합니다.

1.

Kintex-UltraScale Device의 경우 :

DS892 (v1.18) May 21, 2019 - Kintex UltraScale FPGAs Data Sheet: DC and AC Switching Characteristics

DS892 문서의 "Table 51: GTH Transceiver Performance"에 자세히 기술되어 있습니다.

DS892 문서의 "Table 69: GTY Transceiver Performance"에 자세히 기술되어 있습니다.

2.

Virtex-UltraScale Device의 경우 :

DS893 (v1.12) May 23, 2019 - Virtex UltraScale FPGAs Data Sheet: DC and AC Switching Characteristics

DS893 문서의 "Table 51: GTH Transceiver Performance"에 자세히 기술되어 있습니다.

DS893 문서의 "Table 69: GTY Transceiver Performance"에 자세히 기술되어 있습니다.

3.

Kintex-UltraScale+ Device의 경우 :

DS922 문서의 "Table 52: GTH Transceiver Performance"에 자세히 기술되어 있습니다.

DS922 문서의 "Table 64: GTY Transceiver Performance"에 자세히 기술되어 있습니다.

4.

Virtex-UltraScale+ Device의 경우 :

DS923 문서의 "Table 51: GTH Transceiver Performance"에 자세히 기술되어 있습니다.

DS923 문서의 "Table 62: GTM Transceiver Performance"에 자세히 기술되어 있습니다.

5.

Zynq UltraScale+ MPSoC Device의 경우 :

DS925 문서의 "Table 99: GTH Transceiver Performance"에 자세히 기술되어 있습니다.

DS925 문서의 "Table 111: GTY Transceiver Performance"에 자세히 기술되어 있습니다.

6.

Zynq UltraScale+ RFSoC Device의 경우 :

DS926 (v1.5) June 5, 2019 - Zynq UltraScale+ RFSoC Data Sheet: DC and AC Switching Characteristics

DS926 문서의 "Table 100: GTY Transceiver Performance"에 자세히 기술되어 있습니다.

128B/132B

Xilinx Device 중 20 Gbps 이상의 전송속도가 가능한 Gigabit Transceiver가 있습니다. 그러므로 VESA DisplayPort standard 2.0 IP를 FPGA로 설계하고자 하면 구현이 가능함을 예측할 수 있습니다.

그리고 VESA DisplayPort standard 2.0은 Encoding scheme으로 128B/132B가 필요합니다. 하지만 Xilinx Gigabit Transceiver는 128B/132B를 지원하지 않습니다. 따라서 이 부분도 로직으로 설계하여야 하는 문제가 있습니다.

현재 이러한 구현이 가능할 수도 있다는 추정일 뿐 검증되지는 않았습니다.

( 개인적으로는 Xilinx에서 지원하는 64B/66B를 이용하여 User Logic 설계를 통해 128B/132B의 구현 가능성이 매우 높아 보입니다. )

Xilinx에서 공식적으로 128B/132B를 지원하려면 Display Port 2.0 IP가 나오는 시점일 것입니다.

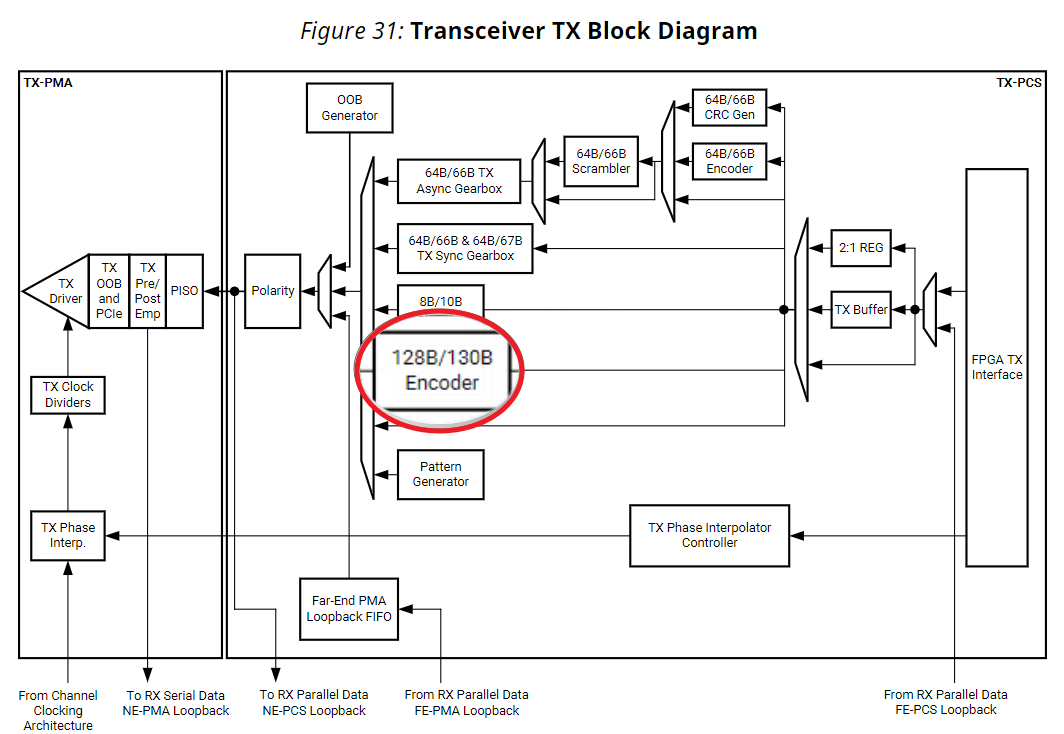

참고로 Xilinx Gigabit Tranceiver에 128B/132B가 있는 것으로 오해하는 경우가 있습니다. 아래 링크는 Xilinx 최근 Device인 Versal의 Gigabit Transceiver에 대한 Datasheet 입니다.

AM002 (v1.0) July 16, 2020 - Versal ACAP GTYTransceivers Architecture Manual

AM002 문서의 Figure 31을 보면 128B/132B가 아닌 128B/130B임을 확인할 수 있으며, 128B/130B는 PCI Express ( PCIe, PCI-e, Peripheral Component Interconnect Express )를 위하여 필요한 부분입니다.

Reference

(PDF) PG230 (v2.2) July 8, 2020 - Video PHY Controller v2.2

(PDF) PG249 October 30, 2019 - HDCP 2.2 v1.0

(PDF) PG224 December 20, 2019 - HDCP 1.x v1.0

(Web-site) VESA(Video Electronics Standards Association)

Video Electronics Standards Association - Wikipedia

Technical standards organization for computer display standards VESA (), formally known as Video Electronics Standards Association, is an American technical standards organization for computer display standards. The organization was incorporated in Califor

en.wikipedia.org

여러분의 FPGA 설계에 조금이라도 도움이 되었으면 합니다.

오늘도 좋은 하루 되세요.

(공감, 구독, 댓글은 저에게 힘이 됩니다!)

Create Date: September 22, 2020

Update Date : July 01, 2022

Posted By : Mouessee

Xilinx 본사는 한국 내에 Corporate and Sales Distributor로 MAKUS를 두고 있습니다.

Xilinx 국내 Corporate and Sales Distributor인 MAKUS는 XIlinx FPGA Device를 기술영업을 통해 판매하며 기술지원이 가능합니다.

MAKUS www.makus.co.kr

관련 BLOG

------------------------------

------------------------------

'Xilinx > IPs' 카테고리의 다른 글

| How to create Xilinx MIG IP for Custom Part (0) | 2022.06.23 |

|---|---|

| MIG IP에서 사용되는 3 종류의 Clock에 대하여 (0) | 2022.05.18 |

| Design Guide for MIG IP (3/3) (1) | 2022.05.16 |

| Design Guide for MIG IP (2/3) (1) | 2022.05.16 |

| Design Guide for MIG IP (1/3) (0) | 2022.05.16 |