Introduction

Xilinx Device에는 Integrated Block for PCI Express가 있어 PCIe 관련 application에 사용됩니다.

하나의 Integrated Block for PCI Express 사용할 경우,

1 lane 구현을 위하여 1 개의 GT( Gigabit Tranceiver )를 사용합니다.

4 lane 구현을 위하여 4 개의 GT( Gigabit Tranceiver )를 사용합니다.

8 lane 구현을 위하여 8 개의 GT( Gigabit Tranceiver )를 사용합니다.

16 lane 구현을 위하여 16 개의 GT( Gigabit Tranceiver )를 사용합니다.

각 Xilinx Device의 Family 별로, 그리고 Package 별로 GT( Gigabit Tranceiver ) 위치에 따라 Integrated Block for PCI Express와 연결하여 사용할 수 있는지, 없는지의 여부를 확인하여야 합니다. 여기서는 Integrated Block for PCI Express와 연결하여 사용할 수 있는 최적화된 GT( Gigabit Tranceiver ) 위치에 대하여 알아보겠습니다.

Test를 위한 PC 사용환경은 다음과 같습니다.

- OS : Windows 10 pro ( version : 21H2 )

- Vivado version : 2022.1

7-Series Integrated Block for PCIe

1.

PG054 - 7 Series Integrated Block for PCIe

위 링크 문서를 보아 주세요.

PG054 문서의 Chapter 4에서 Recommended GT Locations에 대한 정보를 확인할 수 있습니다.

2.

PG054 문서의 Table 4-7을 보면 아래와 같이 Zynq-7000에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

3.

PG054 문서의 Table 4-12을 보면 아래와 같이 Artix-7에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

4.

PG054 문서의 Table 4-11을 보면 아래와 같이 Kintex-7에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

5.

PG054 문서의 Table 4-8, Table 4-9, Table 4-10을 보면 아래와 같이 Virtex-7에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

Table 4-8: Virtex-7 XC7VX485T Recommended GT Locations

Table 4-9: Virtex-7 XC7V585T Recommended GT Locations

Table 4-10: Virtex-7 XC7V2000T Recommended GT Locations

UltraScale Integrated Block for PCIe

1.

PG156 - UltraScale Devices Gen3 Integrated Block for PCIe

위 링크 문서를 보아 주세요.

PG156 문서의 Appx. B에서 Recommended GT Locations에 대한 정보를 확인할 수 있습니다.

2.

PG156 문서의 Figure B-1, Figure B-2, Figure B-3를 보아 주세요.

GT에 대한 Quad Location Rule을 확인할 수 있습니다.

3.

PG156 문서의 Table B-1을 보면 아래와 같이 Virtex UltraScale Devices에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

4.

PG156 문서의 Table B-2을 보면 아래와 같이 Kintex UltraScale Devices에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

UltraScale+ Integrated Block for PCIe

1.

PG213 - UltraScale+ Devices Block for PCIe

위 링크 문서를 보아 주세요.

PG213 문서의 Appx. C에서 Recommended GT Locations에 대한 정보를 확인할 수 있습니다.

2.

PG213 문서의 Figure 139, Figure 140, Figure 141, Figure 142를 보아 주세요.

GT에 대한 Quad Location Rule을 확인할 수 있습니다.

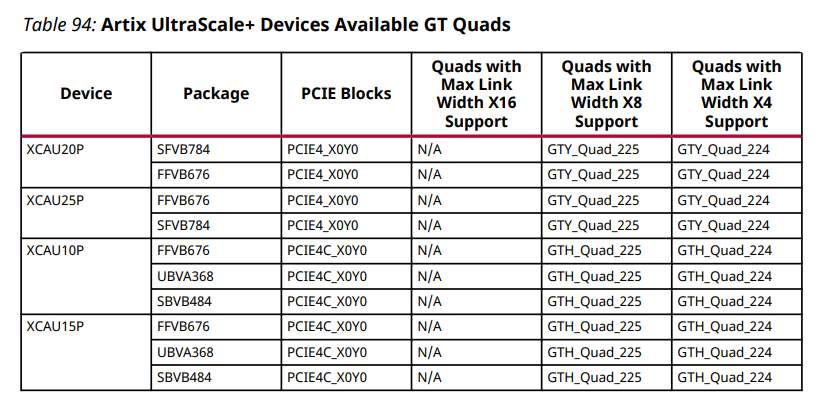

3.

PG213 문서의 Table 94을 보면 아래와 같이 Artix UltraScale+ Devices에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

4.

PG213 문서의 Table 95, Table 96, Table 97, Table 98, Table 99을 보면 아래와 같이 Kintex UltraScale+ Devices에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

5.

PG213 문서의 Table 100 ~ Table 123을 보면 아래와 같이 Kintex UltraScale+ Devices에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

6.

PG213 문서의 Table 124 ~ Table 152을 보면 아래와 같이 Zynq UltraScale+ Devices에서의 Recommended GT locations when using PCIe block를 확인할 수 있습니다.

지금까지 Integrated Block for PCI Express와 연결하여 사용할 수 있는 최적화된 GT( Gigabit Tranceiver ) 위치에 대하여 알아보았습니다.

여러분의 FPGA 설계에 조금이라도 도움이 되었으면 합니다.

오늘도 좋은 하루 되세요.

(공감, 구독, 댓글은 저에게 힘이 됩니다!)

Create Date: July 22, 2022

Posted By: Mouessee

Xilinx 본사는 한국 내에 Corporate and Sales Distributor로 MAKUS를 두고 있습니다.

Xilinx 국내 Corporate and Sales Distributor인 MAKUS는 XIlinx FPGA Device를 기술영업을 통해 판매하며 기술지원이 가능합니다.

MAKUS www.makus.co.kr

관련 BLOG

------------------------------

------------------------------

'Xilinx > IPs' 카테고리의 다른 글

| MIP Pin Mapping Guide for DDR3/4, RDIMMs, LRDIMMs (0) | 2022.08.16 |

|---|---|

| 현재 사용하고 있는 Xilinx IP의 알려진 Bug Issue를 확인하는 방법 (0) | 2022.08.03 |

| How to create COE file & generate ROM (0) | 2022.07.09 |

| GTH의 reference Input Clock과 Data line rate 계산 방법 (4) | 2022.07.06 |

| MIG IP의 Supported DDR4 Memory Parts List (0) | 2022.06.23 |