Introduction

Intel 주도하에 만들어진 PCI Express (Peripheral Component Interconnect Express)는 PC의 main Board에 Graphic Card, Sound Card, TV Card 등의 각종 Expanded Card에 사용되기 위하여 만들어진 규격입니다.

Xilinx FPGA를 사용하여 PCIe Interface를 구현하려면 PCIe + DMA로 구성된 DMA/Bridge Subsystem for PCI Express IP (무료)를 이용하여 설계하면 됩니다.

여기서는 DMA/Bridge Subsystem for PCI Express IP를 사용하여 PCIe End-Point의 구현방법에 대하여 알아보겠습니다.

Test를 위한 PC 사용환경은 다음과 같습니다.

- OS : Windows 10 pro ( version : 20H2 )

- Vivado version : 2020.2.2

- Target Board : Xilinx Kintex-UltraScale FPGA KCU105 Evaluation Kit

PCI Express Link Performance

PCIe의 Version 별 Maximum Link Speed는 다음과 같습니다.

| version | Intrduced Date | Line Code | Transfer Rate |

| 1.0 | 2003 | 8b/10b | 2.5 GT/s |

| 2.0 | 2007 | 8b/10b | 5.0 GT/s |

| 3.0 | 2010 | 128b/130b | 8.0 GT/s |

| 4.0 | 2017 | 128b/130b | 16.0 GT/s |

| 5.0 | 2019 | 128b/130b | 32.0 GT/s |

| 6.0 (planed) | 2021 | PAM4 + 256B + FEC | 64.0 GT/s |

Generating and Implementing Xilinx PCIe Example Design

1.

아래와 같이 원하는 폴더에 Vivado Project를 생성합니다.

2.

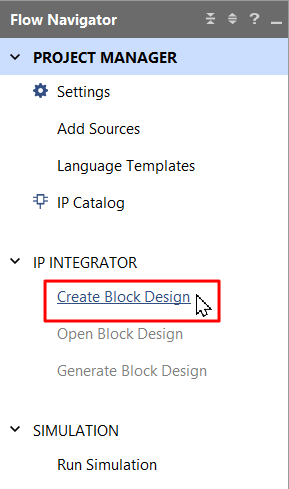

아래와 같이 Flow Navigator 창에서 Create Block Design을 클릭합니다.

3.

아래와 같이 Create Block Design 창이 나타나면 OK 버튼을 클릭합니다.

4.

아래와 같이 Block Design에 DMA/Bridge Subsystem for PCI Express를 Add 합니다.

5.

아래와 같이 Block Design에서 Run Block Automation을 클릭합니다.

Run Block Automation 창이 나타나면 Automation Level을 Subsystem Level로 설정합니다.

PCIe Interface Lane Width를 X1으로 설정합니다. (Board 환경이 PCIe 8-lane이 가능하면 X8을 선택해도 됩니다)

PCIe Interface Maximum Link Speed는 5.0 GT/s (PCIe Gen 2)로 설정합니다.

DMA Interface Option을 AXI Memory mapped로 설정합니다.

Number of XDMA Read Channel H2C를 1로 설정합니다.

Number of XDMA Write Channel C2H를 1로 설정합니다.

이 후, OK 버튼을 클릭합니다.

Ctrl+S를 클릭하여 Block Design을 저장합니다.

6.

Source 창에서 "design_1(design_1.bd)"를 선택한 후 마우스 오른 쪽을 클릭하여 "Create HDL Wrapper"를 클릭합니다.

7.

아래의 내용이 있는 pin.xdc 파일을 생성하여 Alt+A를 클릭하여 Add constarint file을 진행합니다.

set_property PACKAGE_PIN AP8 [get_ports {user_clk_heartbeat[0]}]

set_property PACKAGE_PIN H23 [get_ports user_resetn]

set_property PACKAGE_PIN P20 [get_ports user_lnk_up]

set_property IOSTANDARD LVCMOS18 [get_ports {user_clk_heartbeat[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports user_resetn]

set_property IOSTANDARD LVCMOS18 [get_ports user_lnk_up]

8.

Run Synthesis, Run Implementation, Generate Bitstream를 순차대로 실행합니다.

아래의 링크를 클릭하면 위 Vivado Project 파일을 확인할 수 있습니다.

PCIe_Test.zip

이 후 Windows 10 OS에 XDMA Driver를 설치한 후 PCIe Interface에 대한 PC Demo를 진행하면 됩니다.

How to install XDMA Driver for PCI Express

1.

Windows 10 OS에서 XDMA Driver를 설치하기 전에 반드시 Test Mode로 PC를 재시작하여야 합니다.

Windows 10 OS에서 Test Mode로 Enable하는 방법은 아래의 BLOG를 참고하세요.

[ PCIe ] How to enable / disable "Test Mode" on Windows 10

[ PCIe ] How to enable / disable "Test Mode" on Windows 10

Introduction Xilinx에서 제공하는 DMA for PCI Express (PCIe) Subsystem IP를 사용하려면 개발 PC에 XDMA Windows Driver를 install 하여야 합니다. 하지만 MicroSoft로 부터 인증되지 않은 Driver이기 때문에 개발용 PC에 inst

740280.tistory.com

2.

Windows 10 OS에서 XDMA Driver를 설치하는 방법은 아래의 BLOG를 참고하세요.

[ PCIe ] Xilinx DMA Windows Driver

[ PCIe ] Xilinx DMA Windows Driver

Introduction Xilinx의 DMA for PCI Express (PCIe) Subsystem IP를 사용할 경우, 개발용 PC에 Xilinx DMA Driver를 설치하여야 합니다. 여기서는 Xilinx DMA Driver의 설치 파일과 설치 후에 사용하는 실행파일에 대하여 소

740280.tistory.com

PCIe Demo

1.

작성 중....입니다....

지금까지 DMA/Bridge Subsystem for PCI Express IP를 사용하여 PCIe End-Point의 구현방법에 대하여 알아보았습니다.

여러분의 FPGA 설계에 조금이라도 도움이 되었으면 합니다.

오늘도 좋은 하루 되세요.

(공감, 구독, 댓글은 저에게 힘이 됩니다!)

Feb 21, 2023

Posted By: Mouessee

Xilinx 본사는 한국 내에 Corporate and Sales Distributor로 MAKUS를 두고 있습니다.

Xilinx 국내 Corporate and Sales Distributor인 MAKUS는 XIlinx FPGA Device를 기술영업을 통해 판매하며 기술지원이 가능합니다.

MAKUS www.makus.co.kr

관련 BLOG

------------------------------

------------------------------

'Xilinx > IPs' 카테고리의 다른 글

| [ PCIe ] How to change the ID Initial Values(Vender ID, Device ID, Subsystem Vender ID, Subsystem Device ID) for PCI Express (0) | 2023.02.21 |

|---|---|

| [ PCIe ] Xilinx DMA Windows Driver (0) | 2023.02.21 |

| [ PCIe ] How to enable / disable "Test Mode" on Windows 10 (0) | 2023.02.21 |

| MIP Pin Mapping Guide for DDR3/4, RDIMMs, LRDIMMs (0) | 2022.08.16 |

| 현재 사용하고 있는 Xilinx IP의 알려진 Bug Issue를 확인하는 방법 (0) | 2022.08.03 |