Introduction

ILA (Integrated Logic Analyzer) IP에 매우 느린 clock frequency를 사용할 경우 trigger가 되지 않는 문제가 있습니다.

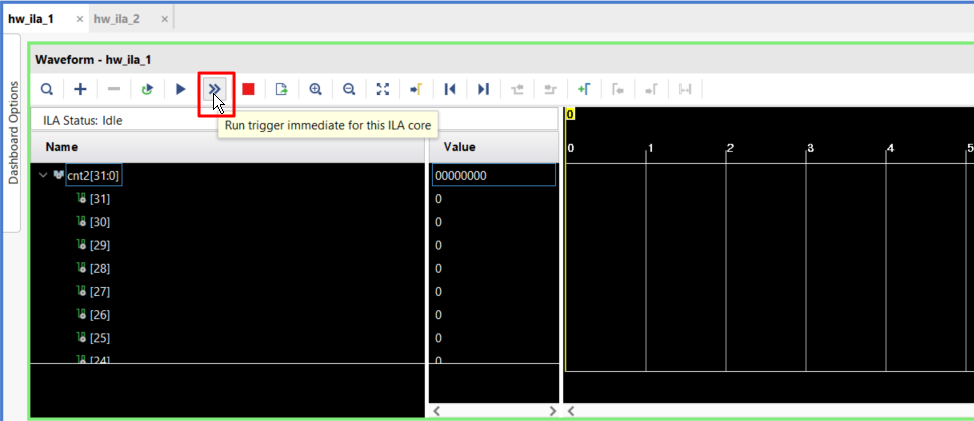

아래의 캡처 화면과 같이 "Run trigger immediate for this ILA core"를 클릭하여도 trigger된 파형이 보이지 않습니다.

여기서는 이러한 현상이 발생하였을 때 문제 해결에 대하여 설명하겠습니다.

Test를 위한 PC 사용환경은 다음과 같습니다.

- OS : Windows 10 pro ( version : 20H2 )

- Vivado version : 2020.2

JTAG clock frequency

1.

아래의 캡처 화면과 같이

Vivado Hardware Manager의 ① download driver를 선택한 후, ② Hardware Target Properties에서 PARAM의 하위 메뉴에 있는 ③ "FREQUENCY"의 value가 "15000000" (15 MHz)으로 설정되어 있음을 확인할 수 있습니다.

(여기서의 Clock frequency가 JTAG clock frequency 입니다.)

2.

PARAM의 하위 메뉴에 있는 "FREQUENCY"의 value를 "5000000" (5 MHz)으로 변경한 후, "Run trigger immediate for this ILA core"를 클릭하면 trigger된 파형을 확인할 수 있습니다.

3.

Debug hub clock frequency는 JTAG clock frequency 보다 적어도 2.5배 이상이 되어야 합니다.

(The JTAG clock is 2.5x times slower than the debug hub clock.)

위에서 설명된 부분은 Debug hub clock frequency가 15 MHz이기 때문에 JTAG clock frequency를 2.5배 이상 느린 5 MHz로 설정하여 trigger된 파형을 확인할 수 있었습니다.

4.

보다 자세한 내용은 아래 링크 문서의 158 ~ 162 페이지의 Debug Cores Clocking Guidelines을 보아 주세요.

UG908 (v2020.2) December 7, 2020 - Vivado Programming and Debugging

지금까지 "Run trigger immediate for this ILA core"를 클릭하여도 trigger된 파형이 보이지 않는 문제에 대하여 알아보았습니다.

여러분의 FPGA 설계에 조금이라도 도움이 되었으면 합니다.

오늘도 좋은 하루 되세요.

(공감, 구독, 댓글은 저에게 힘이 됩니다!)

Create Data: February 23, 2021

Posted By: Mouessee

Xilinx 본사는 한국 내에 Corporate and Sales Distributor로 MAKUS를 두고 있습니다.

Xilinx 국내 Corporate and Sales Distributor인 MAKUS는 XIlinx FPGA Device를 기술영업을 통해 판매하며 기술지원이 가능합니다.

MAKUS www.makus.co.kr

관련 BLOG

------------------------------

------------------------------

To Add HDL to the Block Design

To Add HDL to the Block Design

Introduction Vivado Block Design의 "Add Module to Block Design"에 대하여 알아보겠습니다. 일반적인 RTL source의 경우는 Block Design에서 사용할 수 있는 module 형태로 만들어서 사용이 가능합니다. 물..

740280.tistory.com

Power Guide for Xilinx FPGAs

Introduction Xilinx Device를 사용함에 있어 대부분의 경우, Target Device에 대한 Power 설계에 대한 고민을 많이 합니다. 여기서는 Power Guide for Xilinx FPGAs에 대한 2가지 방법을 설명하려고 합니다...

740280.tistory.com

Configuration Memory Devices List for Xilinx

Configuration Memory Devices List for Xilinx

Introduction Xilinx Devices는 SRAM base (volatile memory)로 되어 있기 때문에 Power-Off 시 저장된 모든 것이 사라집니다. 그런 이유로 외부에 Power-Off 시에도 문제가 없는 Configuration Memory (non-vo..

740280.tistory.com

'Xilinx > Vivado' 카테고리의 다른 글

| How to install a Board Definition file (0) | 2022.08.16 |

|---|---|

| My recommended book for "VHDL" or "Verilog" users (0) | 2022.08.11 |

| To Add HDL to the Block Design (0) | 2022.08.05 |

| How to set up Non-Xilinx Device on JTAG Chain (0) | 2022.08.02 |

| Vivado ML Edition의 종류와 서로 간의 차이점 및 가격 (0) | 2022.07.05 |